本文今天带大家学习一下 从静态时序分析到SDRAM时序收敛的时序。

”零基础 FPGA 静态时序分析 SDRAM时序收敛 文章 单片机 FPGA“ 的搜索结果

本文今天带大家学习一下 从静态时序分析到SDRAM时序收敛的时序。

9.3 DDR SDRAM接口 DDR SDRAM接口可以看作是上一节中所介绍的SRAM接口的一种扩展。就像SRAM接口一样,有两条主要的总线,图9-9说明了DUA和SDRAM之间的总线及其方向。由命令、地址和控制引脚(通常称为CAC)组成的第一...

摘 要:本文对高速、高精度大容量数据采集板卡所采用的SDRAM控制器技术进行了讨论,详细介绍了基于FPGA的SDRAM控制器的设计、命令组合以及设计仿真时序,并将该技术应用于基于PCI总线的100MHz单通道 AD9432高速大...

FPGA知识点笔记(一)

标签: fpga开发

(1)FPGA(Fied Programmable Gate Array),现场可编程门阵列,它是在PLA、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路ASIC领域中出现的一种半定制电路而出现的。既解决了定制电路的不足...

FPGA-Vivado

标签: fpga开发

FPGA入门笔记

关注我们 更多精彩等你发现! ▌本文来源:电子发烧友 ...首先,“嵌入式”这是个概念,准确的定义没有,各个书上都有各自的定义。但是主要思想是一样的,...MCU俗称”单片机“经过这么多年的发展,早已不单单只...

1、简述建立时间和保持时间 建立时间Tsu(setup):触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。 保持时间Th(hold):触发器在时钟上升沿到来之后,其数据输入端的数据必须保持...

SDRAM作为嵌入式系统中的重要内存技术之一,以其大容量、高速度和同步操作的特性在多个领域发挥着关键作用。通过深入理解SDRAM的工作原理和特性,并结合具体的开发经验和应用场景进行阐述,我们希望能够帮助读者更加...

更新日志: 时间 更新内容 ...Mculover666,一个喜欢玩板子的...CSDN用于日常开发中的文章记录与分享 个人网站用于系列教程连载:http://www.mculover666.cn Github目前也收获了100多个Start:https://github.com/M

DDR 控制器继续加入延时后发送DQS 信号, DDR4 芯片在DQS上升沿采样CK 信号, 发现CK=1, 则等待一段时间后, DDR4芯片将DQ 信号置高。RESET 释放拉高后, 需要等500US, CKE 才置高有效, 在这个期间DDR4 芯片完成...

1、简述建立时间和保持时间 建立时间Tsu(setup):触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。 保持时间Th(hold):触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变...

掌握了FPGA设计,单板硬件设计就非常容易(不是系统设计),特别是上大学时如同天书的逻辑时序图,看起来就非常亲切。但FPGA入门却有一定难度,因为它不像软件设计,只要有一台计算机,几乎就可以完成所有的设计。F...

1.FPGA不是编程语言,而是一种可综合的硬件描述语言。 2.Verilog 支持两种进程initial和always进程 3.阻塞与非阻塞指的相对于进程本身而言的。 4.使用进程模块的电路类型: 组合电路-----对组合逻辑中...

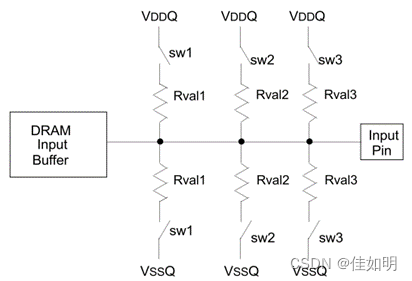

DDR3电路设计

推荐文章

- 大数据和云计算哪个更简单,易学,前景比较好?_大数据和云计算哪个好-程序员宅基地

- python操作剪贴板错误提示:pywintypes.error: (1418, 'GetClipboardData',线程没有打开的剪贴板)...-程序员宅基地

- IOS知识点大集合_ios /xmlib.framework/headers/xmmanager.h:66:32: ex-程序员宅基地

- Android Studio —— 界面切换_android studio 左右滑动切换页面-程序员宅基地

- 数据结构(3):java使用数组模拟堆栈-程序员宅基地

- Understand_6.5.1175::New Project Wizard_understand 6.5.1176-程序员宅基地

- 从零开始带你成为MySQL实战优化高手学习笔记(二) Innodb中Buffer Pool的相关知识_mysql_global_status_innodb_buffer_pool_reads-程序员宅基地

- 美化上传文件框(上传图片框)_文件上传框很丑-程序员宅基地

- js简单表格操作_"var str = '<table border=\"5px\"><tr><td>序号</td><-程序员宅基地

- Power BI销售数据分析_powerbi汇总销售人员业绩包括无销售记录的人-程序员宅基地